Exploring the Performance/Power/Resilience (PPR) Co-Design Options for Throughput-Oriented Architecture

> Xin Fu<sup>†</sup> Jingweijia Tan<sup>†</sup> Shuaiwen Leon Song<sup>\*</sup>

University of Houston<sup>†</sup> Pacific Northwest National Laboratory<sup>\*</sup>

UNIVERSITY of **HOUSTON**

#### **Throughput-Oriented Architecture: GPGPUs**

- Graphics Processing Units (GPUs)

- Support thousands of concurrent threads

- High computational throughput

- GPGPUs become a popular platform for general-purpose HPC applications

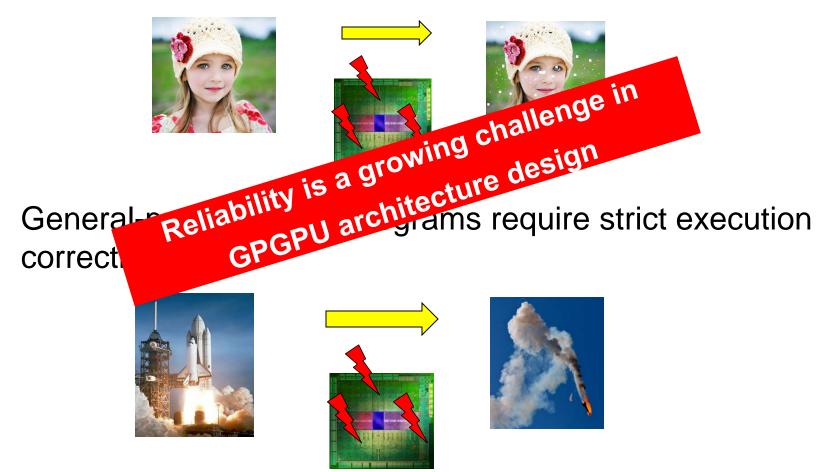

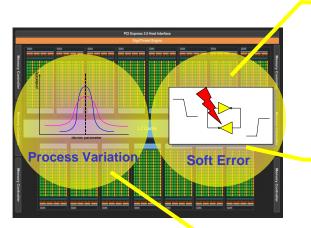

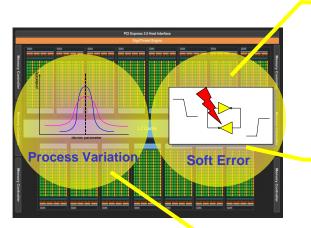

#### **Reliability Challenges in GPGPUs**

- GPUs is originally designed for graphics applications

- Error detection and fault tolerance are ignored!

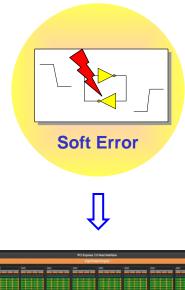

# Hardware Reliability Challenge: Soft Error

- One of the most severe reliability threats

- Caused by energetic particles

Flip the device state (0→1 or 1→0)

- Leads to data corruption

- Circuits are not damaged

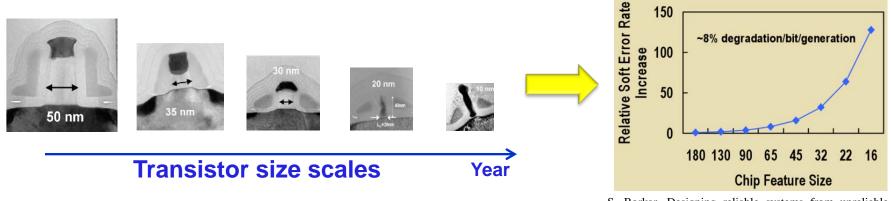

S. Borkar, Designing reliable systems from unreliable components: the challenges of transistor variability and degradation, IEEE Computer Society, 2005

Soft error rate increases significantly as technology scales down

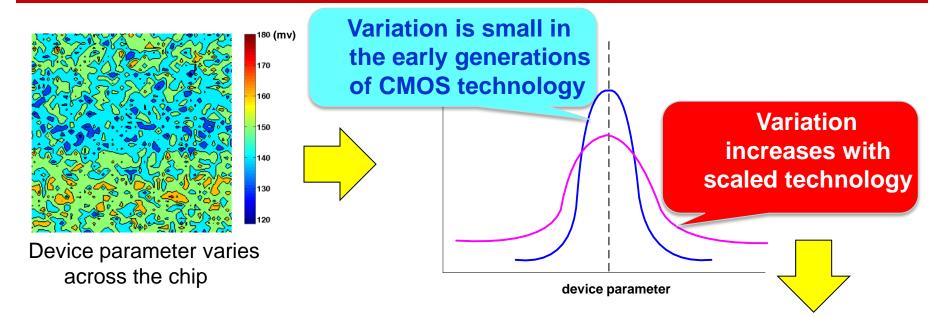

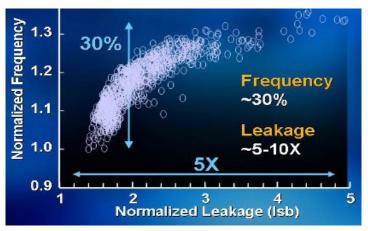

#### Hardware Reliability Challenge: Process Variation (PV)

- PV dramatically reduce GPUs F<sub>max</sub>

- F<sub>max</sub> is limited by the slowest critical path

- Numerous critical path in GPUs

S. Borkar, et al. Parameter variations and impact on circuits and microarchitecture, DAC'03

#### **Performance/Power/Resilience Co-Design**

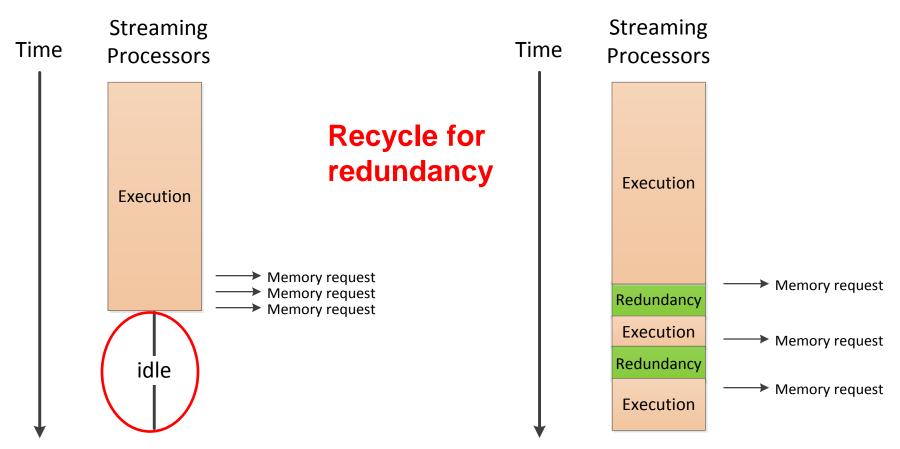

RISE: *R*ecycling the streaming processors *I*dle time for *S*oft-*E*rror detection => performance/resilience co-design

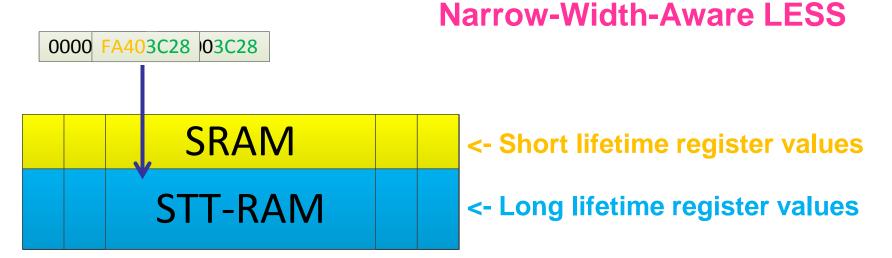

LESS: LEverage reSistive memory to

enhance the Soft-error robustness

=> performance/power/resilience co-design

Mitigating the Susceptibility of GPGPUs Register File to Process Variations => performance/resilience co-design

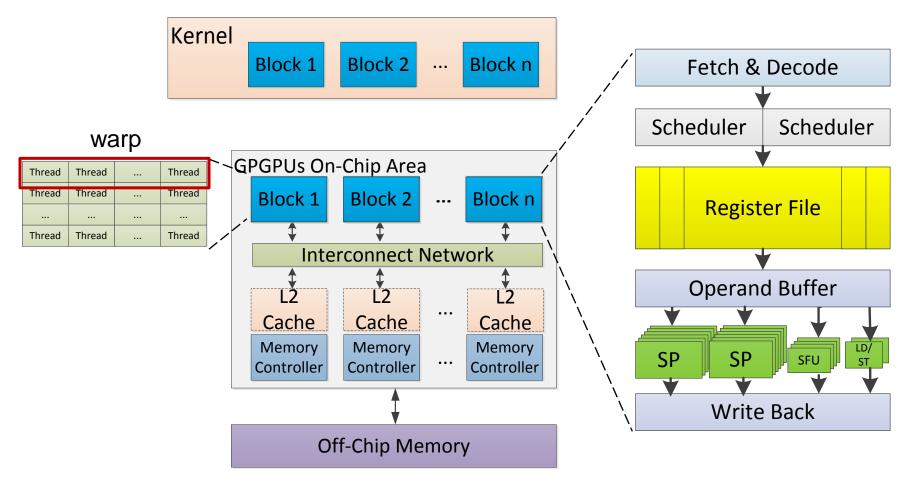

### **Background: GPGPUs Architecture**

SM: Streaming Multiprocessor

- Introduction and Background

- RISE: *R*ecycling the streaming processors *I*dle time for *S*oft-*E*rror detection

- LESS: LEverage reSistive memory to enhance the robustness

- Mitigating the Susceptibility of GPGPUs Register File to Process Variations

- Conclusions

#### **RISE**

- Warps in the same SM exhibit similar execution progress

- Memory requests are sent at similar time

RISE: Recycle the SPs idle time caused by long-latency memory accesses for redundancy

RISE: *R*ecycling the streaming processors *I*dle time for *S*oft-*E*rror

detection

Introduction and Background

- LESS: LEverage reSistive memory to enhance the robustness

- Mitigating the Susceptibility of GPGPUs Register File to Process Variations

- Conclusions

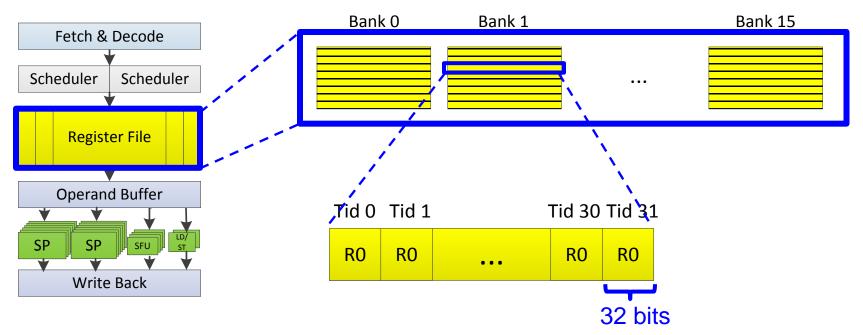

## **Register File (RF) in GPGPUs**

- The extreme multithreading requires a sizeable register

file

Fetch & Decode

- 3.75MB in NVIDIA Kepler [NVIDIA, 2012]

6MB in AMD Cayman [Kanter, 2010]

We focus on the soft-error reliability and power co-optimization for GPGPUS RF

- Exposes them to the particle strikes

- RF is *power-hungry* [Leng, 2013]

- Large dynamic and leakage power due to large size

SFU

Write Back

LD/ST

SP

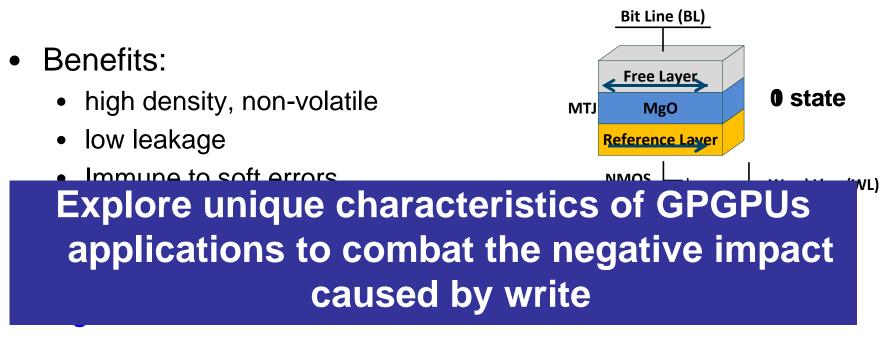

## **Resistive Memory**

- Spin-Transfer Torque RAM (STT-RAM)

- Uses Magnetic Tunnel Junction (MTJ) as the data storage device

Disadvantages: long write delay and high write energy

All STT-RAM RF=> 70% performance ↓, 14% energy↑

- LESS: co-optimizes soft-error reliability and power consumption for GPGPUs RF

- A small amount of long lifetime registers are the major vulnerability contributor Lifetime-Aware LESS

- A lot of STT-RAM writes are narrow-width

- Introduction and Background

- RISE: *R*ecycling the streaming processors *I*dle time for *S*oft-*E*rror detection

- LESS: LEverage reSistive memory to enhance the robustness

- Mitigating the Susceptibility of GPGPUs Register File to Process Variations

- Conclusions

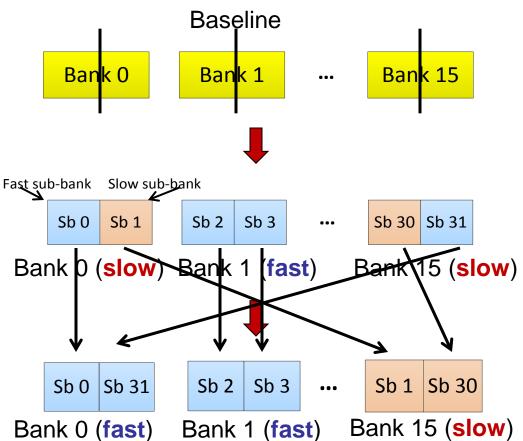

## **Background: Multi-Banked RF in GPGPUs**

- Highly-banked (e.g., 16) to provide high bandwidth

- Multiple register operands required by one instruction can be accessed simultaneously

- Each entry is composed of 32 same-named registers

- Threads execute in SIMD mode

- -1 warp = 32 threads

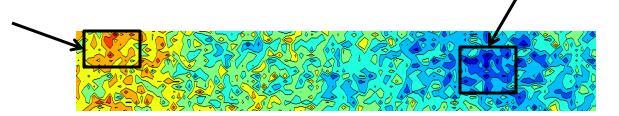

## **PV Impact on GPGPUs Register File (RF)**

- GPGPUs RF

- Large size

- Highly banked

- Contains numerous critical paths

- RF is vulnerable to PV impact

V<sub>th</sub> variation map of GPGPUs RF

## **Frequency Optimization under PV**

- Frequency Optimizations for GPGPUs RF

under PV

Baseline

- Variable-Latency

Sub-Bank

- RF Bank Re Organization

- 15% frequency improvement

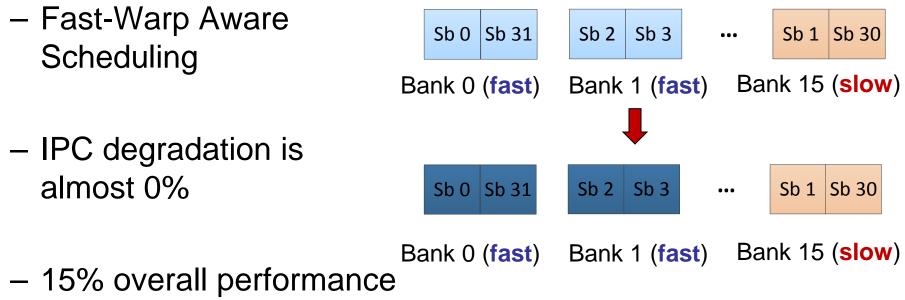

## **IPC improvement under PV**

• Mitigating the *IPC* Degradation under PV

15% overall performance improvement

- Introduction and Background

- RISE: *R*ecycling the streaming processors *I*dle time for *S*oft-*E*rror detection

- LESS: LEverage reSistive memory to enhance the robustness

- Mitigating the Susceptibility of GPGPUs Register File to Process Variations

- Conclusions

#### **Performance/Power/Resilience Co-Design**

RISE: *R*ecycling the streaming processors *I*dle time for *S*oft-*E*rror detection => performance/resilience co-design

LESS: LEverage reSistive memory to

enhance the Soft-error robustness

=> performance/power/resilience co-design

Mitigating the Susceptibility of GPGPUs Register File to Process Variations => performance/resilience co-design