Prometheus: Scalable and Accurate Emulation of Task-Based Applications on Many-Core Systems

GOKCEN KESTOR, ROBERTO GIOIOSA, DANIEL CHAVARRÍA-MIRANDA

2015 Workshop on Modeling & Simulation of Systems and Applications

# Exascale parallel programming models

Exascale systems will achieve high performance through high level of parallelism

- O(1k-10k) cores per node

- O(billion) concurrent threads

- Task-based programming models are a promising way to program exascale applications

- Applications are divided into a myriad of small tasks

- The system is oversubscribed with tasks (N<sub>tasks</sub> >> N<sub>cores</sub>)

- e.g., Cilk++, Intel TBB, Charm++, etc.

There are no tools to model these systems (hardware and software) at the level of scalability required.

August 14, 2015

#### Simulators/Emulators landscape Pacific Northwest Proudly Operated by Battelle Since 1965 1-O(100) Cores 1-O(1000) Cores 1-8 Cores 1-1k Cores Error < 25%Error < 10%Error ? Error ? Cycle-Cycle-**Discrete-Full-system** approximate accurate event emulators simulators simulators emulators Prometheus Model Employ Trace can be manipulated Accura **Pros**: Scalable **Pros**: F Pros: A **Pros:** F **<u>Cons</u>**: Reordering change the app behavior Cons: Cons: Cons: S Cores: 1-thousands Cores: Cores: Cores: **<u>App</u>**: C App: OMP, MPI **App**: S **App**: C **Ex**: BigSim, DIMEMAS Ex: Ge Ex: Zsi Ex: KV

## **Prometheus**

Key Observation: When modeling parallel applications on large systems, performance is largely dominated by runtime and synchronization effects

- Fast enough to emulate future exascale nodes

- Accurate and reliable results

- Modular, swap components in and out

- Model non-determinism of task-based applications

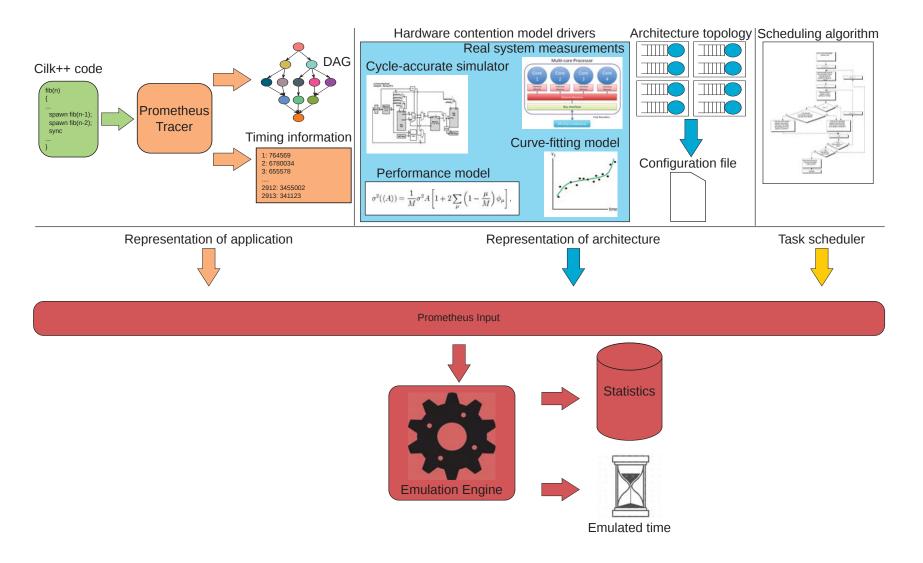

## **Prometheus Architecture**

Pacific Northwest NATIONAL LABORATORY Proudly Operated by Battelle Since 1965

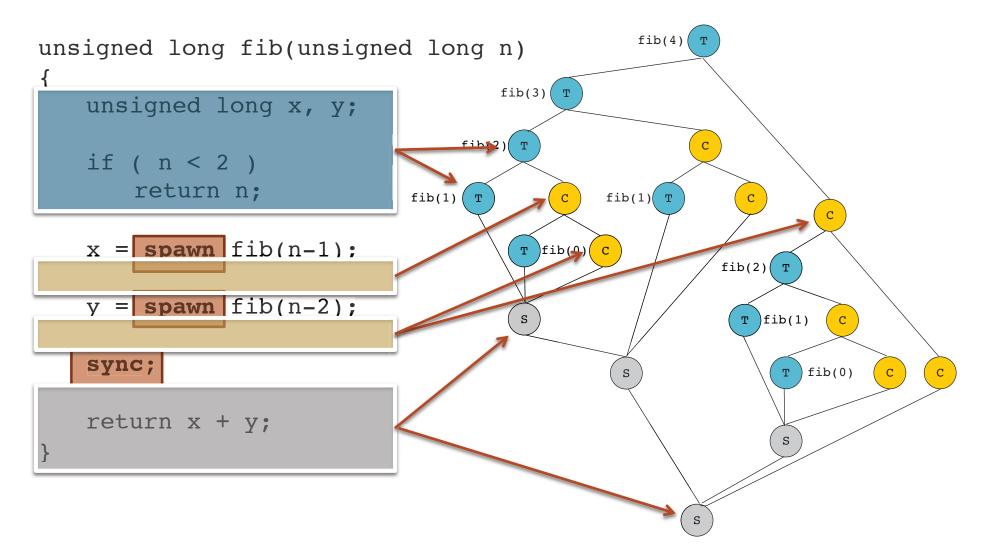

#### **DAG tracer**

The DAG is extracted from single thread execution

Difficult and not necessary to extract a DAG from parallel execution

DAGs do not depend on the level of execution parallelism

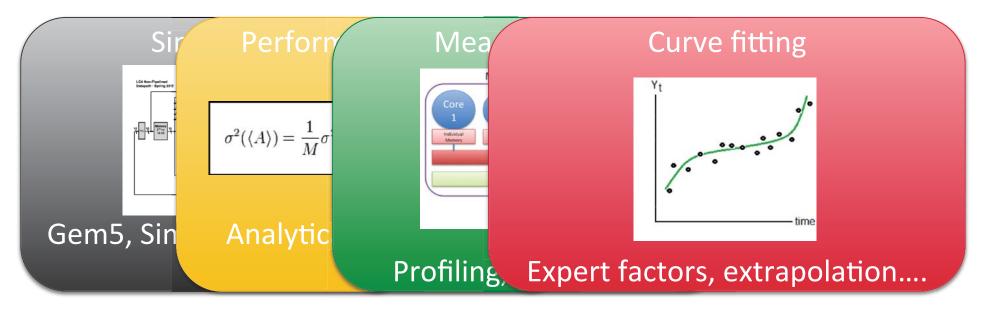

Hardware contention in multi-core and multi-threaded processor is modeled by the contention module.

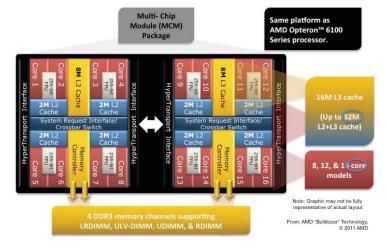

# Validation – Experimental setup

- Modeling a AMD Interlagos systems\*

- 2 processors chips

- 4 modules, 4 cores/module, 2 threads/core

- 32 threads total

- 64 GB DRAM, 4 NUMA domains

- Cilk++ task-based applications

- Random work-stealing, work-first scheduler

| Application | Configuration                    | Number of tasks |

|-------------|----------------------------------|-----------------|

| Fib         | n = 35                           | 74,651,756      |

| Heat        | nt = 200, nx = 4096*4, ny = 1024 | 1,234,945       |

| Integrate   | xMax = 5000                      | 193,385,368     |

| Jacobi      | n = 1024, steps = 100            | 139,809,901     |

| MatrixMul   | n = 256                          | 71,902,351      |

| QuickSort   | n = 75000000                     | 152,452,586     |

| Parameter          | Same core | Local NUMA | Remote NUMA |

|--------------------|-----------|------------|-------------|

| Successful steal   | 7555      | 9135       | 10635       |

| Unsuccessful steal | 1148      | 1199       | 1382        |

\* Results for Intel MIC (244 hardware threads) in the paper.

# Validation – Results

| RMin 🕇           | qSort | MMul   | Jacobi | Integ. | Heat  | Fib   |       | Ν  |

|------------------|-------|--------|--------|--------|-------|-------|-------|----|

| ×                | 5.39  | 104.94 | 24.46  | 53.86  | 29.20 | 53.75 | RMin  | 8  |

| T                | 5.32  | 105.50 | 24.53  | 52.10  | 29.03 | 54.10 | Emu   |    |

| RMax             | 6.17  | 106.24 | 25.21  | 54.40  | 30.01 | 54.88 | RMax  |    |

|                  | -1.28 | 0.00   | 0.00   | -3.28  | -0.58 | 0.00  | Error |    |

| X                | 3.86  | 52.28  | 12.86  | 52.43  | 18.46 | 26.39 | RMin  | 16 |

|                  | 3.77  | 52.54  | 12.93  | 50.61  | 18.36 | 26.52 | Emu   |    |

|                  | 4.07  | 52.62  | 12.96  | 52.88  | 19.03 | 26.53 | RMax  |    |

| Generally <4%,   | -2    | 0.00   | 0.00   | -3.46  | -0.54 | 0.00  | Error |    |

| max 5.2%         | 4     | 29.44  | 8.19   | 37.14  | 17.95 | 17.93 | RMin  | 32 |

|                  | 4     | 29.44  | 8.13   | 35.87  | 18.08 | 17.99 | Emu   |    |

| vo exceptions on | 4     | 29.54  | 8.36   | 37.40  | 18.89 | 18.15 | RMax  |    |

| MIC (6.97 and    | 5     | 0.00   | -0.82  | -3.43  | 0.00  | 0.00  | Error |    |

| 10.16%)          |       |        |        |        |       |       |       |    |

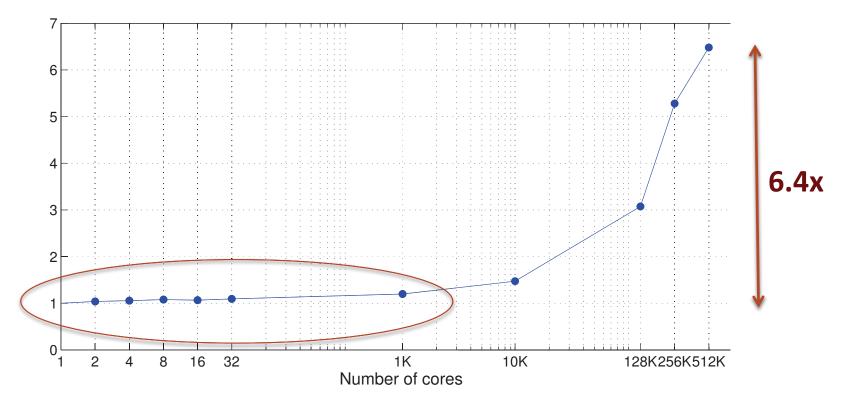

## Performance

- Minimum slowdown up to 1,024 cores

- 6.4x slowdown at 512k cores

- Emulation completed in 11.5 hours

- Idle cores slow down emulation!

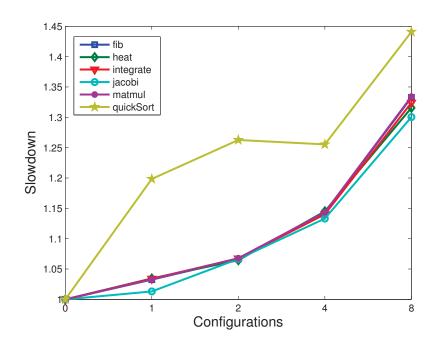

## **Case study 1: Power-constrained systems**

Pacific Northwest NATIONAL LABORATORY Proudly Operated by Battelle Since 1965

- Emulate the behavior of heterogeneous, power-constrained exascale systems

- 1,024 total cores, 16 voltage islands, 64 cores/island

- Varying the number of voltage islands in low-power mode

- Low-power mode cores run at ½ max frequency

- Automatic task balancing contains performance degradation

Low-power

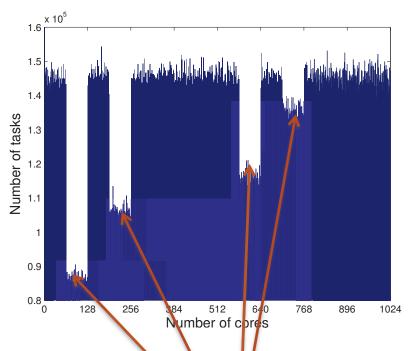

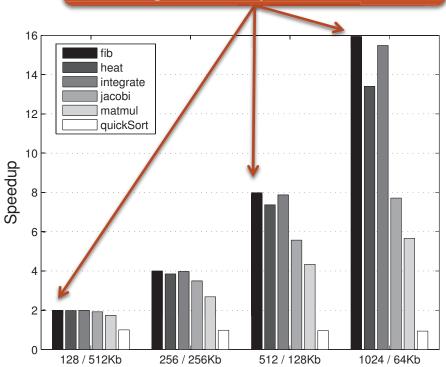

# Case study 2: Reduced per-core cache

Assume exascale architectures with many-cores on a chip but reduced per-core cache

Use Gem5 SE as hardware contention driver to model multicore ARM processor

- 16 processor chips

- 4 MB last-level cache per processor chip

- 4 to 64 cores per processor chip

Parallelism makes up for reduced single-thread performance

Note: we could not run Cilk++ apps on Gem5 SE

Modeling exascale systems will require new scalable tools

Task-based programming models are non-deterministic

Prometheus: a fast, scalable, modular emulator for task-based applications

Prometheus scales up to 512k cores in 11.5h (6.4x slowdown)

Future work: add network, power, resilience...

# **Acknowledgements & more information**

- Work sponsored by DOE ASCR under the Beyond the Standard Model (BSM) project

- Kestor G, R Gioiosa, and D Chavarría-Miranda. 2015. "Prometheus: Scalable and Accurate Emulation of Task-Based Applications on Many-Core Systems." In IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS 2015).

- Akhmetova D, G Kestor, R Gioiosa, S Markidis, and E Laure. 2015. "On the application task granularity and the interplay with the scheduling overhead in many-core shared memory systems." To Appear in IEEE Cluster 2015