Hybrid Computing Technologies

Hybrid Architectures

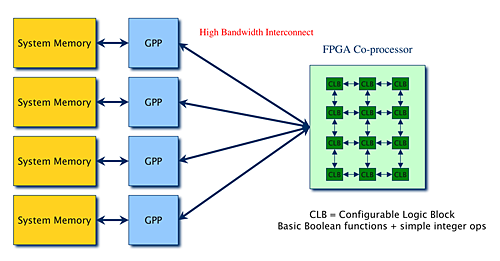

Computer architectures for HPC are shifting away from standard, cache-based, general-purpose microprocessors, which have dominated the field for the last 10-15 years. One of the reasons for this trend is the diminishing increase in performance obtained from traditional scaling due to Moore's Law. Vendors are pursuing two strategies to address this issue: increasing the levels of parallelism provided by a single chip by adding replicated processor cores on the same die; and complementing general-purpose microprocessors with specialized processing elements such as reconfigurable computing fabrics (i.e., Field Programmable Gate Arrays [FPGAs]), on-chip parallel processing elements designed for compute-intensive applications with private, software-controlled local memories (IBM's Synergistic Processing Elements (SPEs) in the Cell Processor), special-purpose processors being used for more general processing tasks (i.e., Graphics Processing Units [GPUs] used for arithmetic computations), as well as other architectures.

Abstract Hybrid Architecture

FPGA-based Acceleration

Current Focus Areas

- Proteomics data analysis

- Power grid analysis